# LCD controller IP

**Marcos Vinicius Silva Oliveira**

# **Summary**

- Lab3 block diagram

- •Modes of operation

- Constraints

- **LCD** controlleer IP

- Freatures

- Register Map

- Top level connections

- •ILI 4391 connections

- Block diagam

- Simulation Results

- Logic Analyser results

- Demo

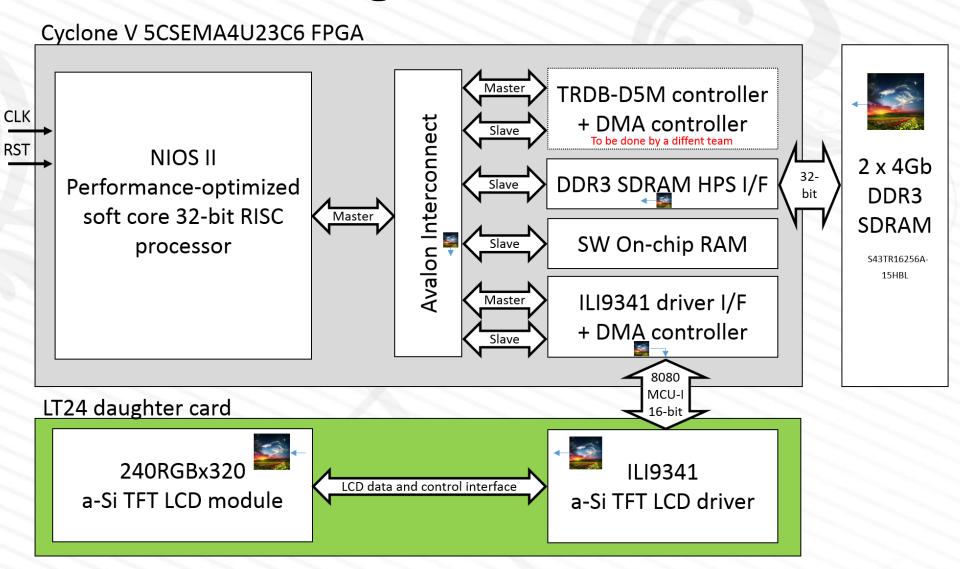

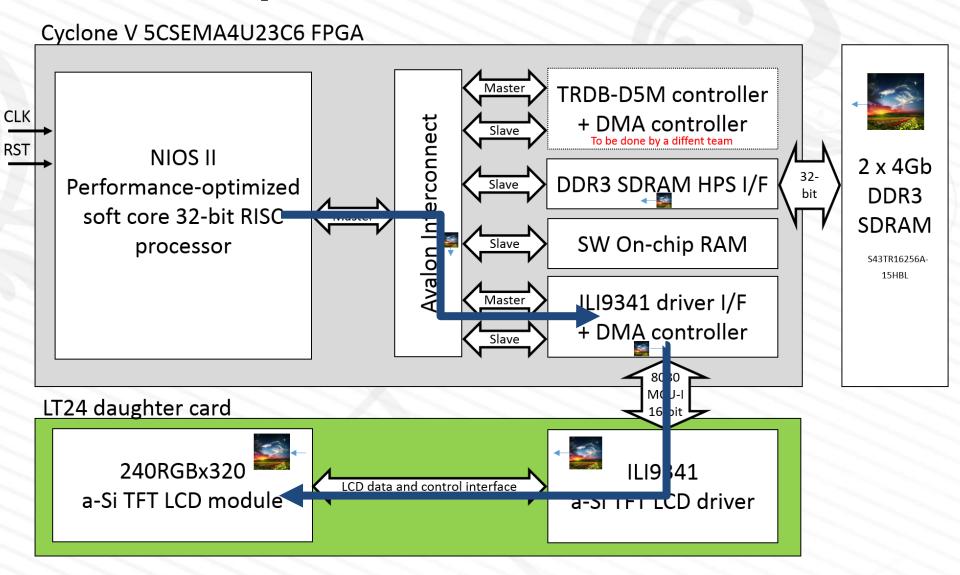

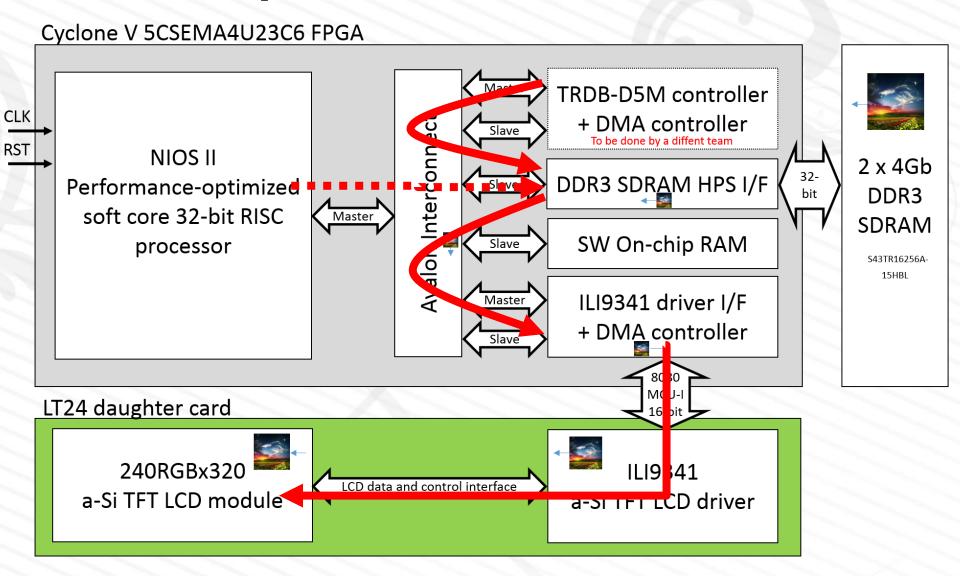

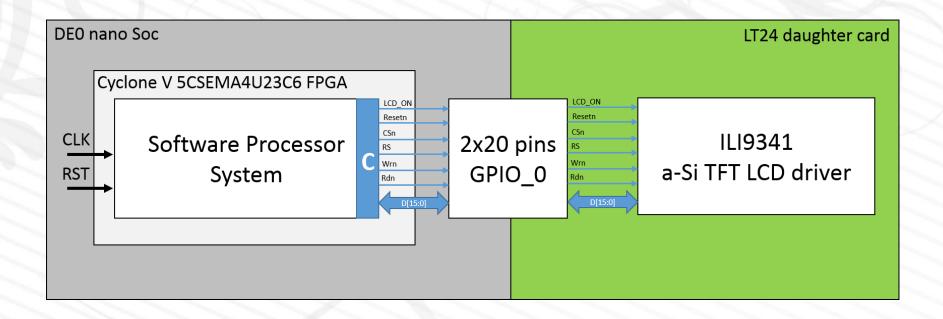

### Lab3 block diagram

#### Mode of operation A

#### Mode of operation B

#### **Constraints**

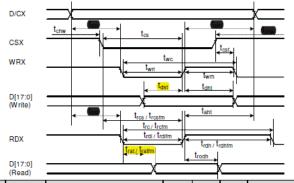

#### 18.3 AC Characteristics

18.3.1 Display Parallel 18/16/9/8-bit Interface Timing Characteristics (8080- I system)

| Signal                                    | Symbol   | Parameter                          | min | max | Unit | Description                               |  |

|-------------------------------------------|----------|------------------------------------|-----|-----|------|-------------------------------------------|--|

| DCX                                       | tast     | Address setup time                 | 0   | -   | ns   |                                           |  |

| DOX                                       | taht     | Address hold time (Write/Read)     | 0   | -   | ns   |                                           |  |

| CSX                                       | tchw     | CSX "H" pulse width                | 0   | -   | ns   |                                           |  |

|                                           | tcs      | Chip Select setup time (Write)     | 15  | -   | ns   |                                           |  |

|                                           | tres     | Chip Select setup time (Read ID)   | 45  |     | (NS) |                                           |  |

|                                           | (trosfm) | (Chip Select setup time (Read FM)) | 355 |     | ns   |                                           |  |

|                                           | tcsf     | Chip Select Wait time (Write/Read) | 10  | -   | ns   |                                           |  |

| WRX                                       | twc      | Write cycle                        | 66  | -   | ns   | must be $4 \times 20 \text{ ns} = 8$      |  |

|                                           | twrh     | Write Control pulse H duration     | 15  | -   | ns   |                                           |  |

|                                           | twrl     | Write Control pulse L duration     | 15  | -   | ns   |                                           |  |

| RDX (FM)                                  | trcfm    | Read Cycle (FM) (450)              |     |     | ns   |                                           |  |

|                                           | trdhfm   | (Read Control H duration (FM))     | 90  |     | ns   |                                           |  |

|                                           | trdlfm   | (Read Control L duration (FM))     | 355 |     | ns   |                                           |  |

| (RDX (ID))                                | (tre     | (Read cycle (ID))                  | 160 |     | ns   |                                           |  |

|                                           | (trdh)   | Read Control pulse H duration      | 90  |     | ns   |                                           |  |

|                                           | (trdl)   | (Read Control pulse L duration)    | 45  |     | (NS) |                                           |  |

| D[17:0],<br>D[15:0],<br>D[8:0],<br>D[7:0] | tdst     | Write data setup time              | 10  | -   | ns   | For maximum CL=30pF<br>For minimum CL=8pF |  |

|                                           | tdht     | Write data hold time               | 10  | -   | ns   |                                           |  |

|                                           | trat     | Read access time                   | •   | 40  | ns   |                                           |  |

|                                           | tratfm   | Read access time                   |     | 340 | ns   |                                           |  |

|                                           | trod     | Read output disable time           | 20  | 80  | ns   |                                           |  |

Note: Ta \_ - 30 to 70 °C VDDL-1 65V to 3 3V VCL-2 5V to 3 3V VSS\_0V

Maximum frame refresh rate:

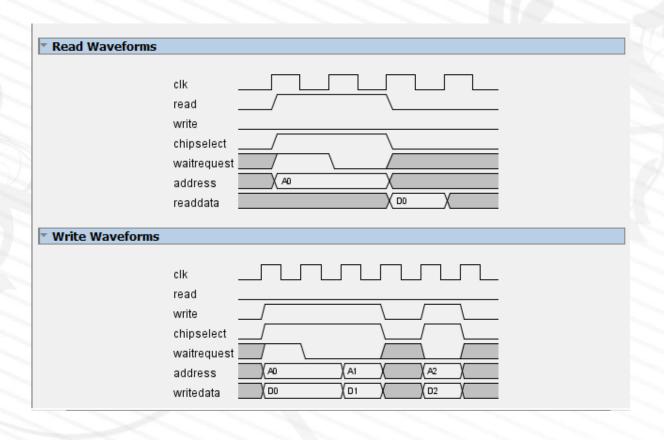

- Control signals synchronous with Avalon clock -> 50 MHz

- Writing cycles should last 4 clock cycles fo meet the min twc of 66 ns.

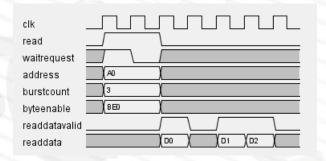

- Read cycles should last at least 9 cycles to reach the trcfm of 450 ns.

- Dummy data in read cycle

- Handled in SW as performance not important for read accesses

$$\frac{50 \text{ MHz}}{4 \times 240 \times 320} = 162.76 \text{ Hz}.$$

# **Freatures**

| LCD controller IP features      |                                                                          |  |  |  |  |  |  |

|---------------------------------|--------------------------------------------------------------------------|--|--|--|--|--|--|

| Modes of operation              | A: Processor writes data to ILI9341 B: DMA engine writes data to ILI9341 |  |  |  |  |  |  |

| ILI9341 write access            | Yes                                                                      |  |  |  |  |  |  |

| ILI9341 read access             | Yes                                                                      |  |  |  |  |  |  |

| Multiple buffering              | Implemented in SW                                                        |  |  |  |  |  |  |

| Number of buffers               | Not limited by the IP (limited by off-chip memory)                       |  |  |  |  |  |  |

| Max Frame rate                  | 162.76 Hz                                                                |  |  |  |  |  |  |

| Minimal interval between frames | configurable by PUSHBUTTONS / SW                                         |  |  |  |  |  |  |

| Frame receiveid Ack             | Accessible by the Arduino interface D0 pin                               |  |  |  |  |  |  |

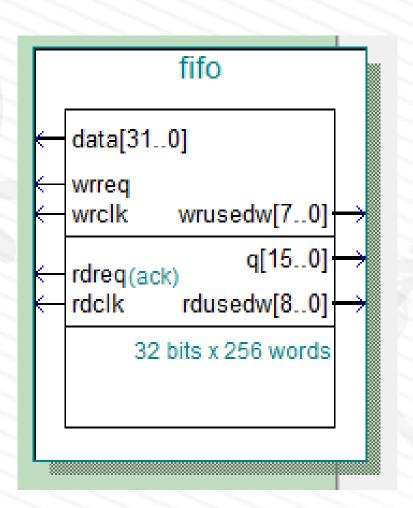

| FIFO size                       | 256 words (1 M4K)                                                        |  |  |  |  |  |  |

| StartAdress                     | configurable by SW                                                       |  |  |  |  |  |  |

| EndAddress                      | configurable by SW                                                       |  |  |  |  |  |  |

| DMA Request Mode                | New request only after current is finished                               |  |  |  |  |  |  |

| DMA burst length                | configurable by SW (2-256) (could be 1024 if FIFO up)                    |  |  |  |  |  |  |

| FIFO threshold                  | configurable by SW                                                       |  |  |  |  |  |  |

| IRQ support                     | Yes                                                                      |  |  |  |  |  |  |

| IRQ masking                     | configurable by SW                                                       |  |  |  |  |  |  |

| DMA sync rst                    | set by SW                                                                |  |  |  |  |  |  |

| Debug LCD FSM                   | Yes                                                                      |  |  |  |  |  |  |

| Debug DMA FSM                   | Yes                                                                      |  |  |  |  |  |  |

| Debug DMA Addr                  | Yes                                                                      |  |  |  |  |  |  |

| Debug DMA RX DATA               | Yes                                                                      |  |  |  |  |  |  |

| Debug Pushbuttons               | Yes                                                                      |  |  |  |  |  |  |

# Register Map

Table 1: LCD controller IP Register Map

| 32-bit word offset | Byte offset | Type         | Register Name (W $/$ R)        | Default Value |

|--------------------|-------------|--------------|--------------------------------|---------------|

| 0x00               | 0x00        | W            | SendCommand / -                | 0x0           |

| 0x01               | 0x04        | RW           | SendData / ReadsData           | 0x0           |

| 0x02               | 0x08        | RW           | LCDOn                          | 0x0           |

| 0x03               | 0x0C        | RW           | LCDResetN                      | 0x0           |

| 0x04               | 0x10        | RW           | - / DataReadFromILI9341        | -             |

| 0x05               | 0x14        | RW           | MaskIRQ(1)                     | 0x0           |

| 0x05               | 0x14        | RW           | ForceIRQ(0)                    | 0x0           |

| 0x06               | 0x18        | RW           | DmaIrqAck / LCDFSMState        | 0x0           |

| 0x07               | 0x1C        | RW           | DmaSyncRst(1) / DmaFSMState(1) | 0x0           |

| 0x07               | 0x1C        | RW           | DmaFire(0) / regDmaFSMState(0) | 0x0           |

| 0x08               | 0x20        | RW           | DmaStartAddr/DmaAddr           | 0x0           |

| 0x09               | 0x24        | RW           | DmaEndAddr/ DmaRxCount         | 0x0           |

| 0x0A               | 0x28        | RW           | DmaBurstCount                  | 0x0           |

| 0x0B               | 0x2C        | RW           | DmaFifoThreshold               | 0x0           |

| 0x0C               | 0x30        | RW           | OpMode                         | 0x0           |

| 0x0D               | 0x34        | $\mathbf{R}$ | - / KEY_N                      | -             |

#### LCD controller IP

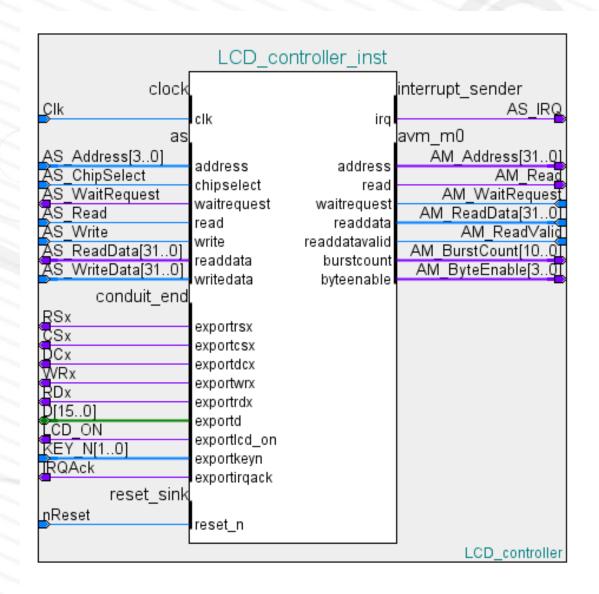

# ILI9341 <-> LCD controller IP

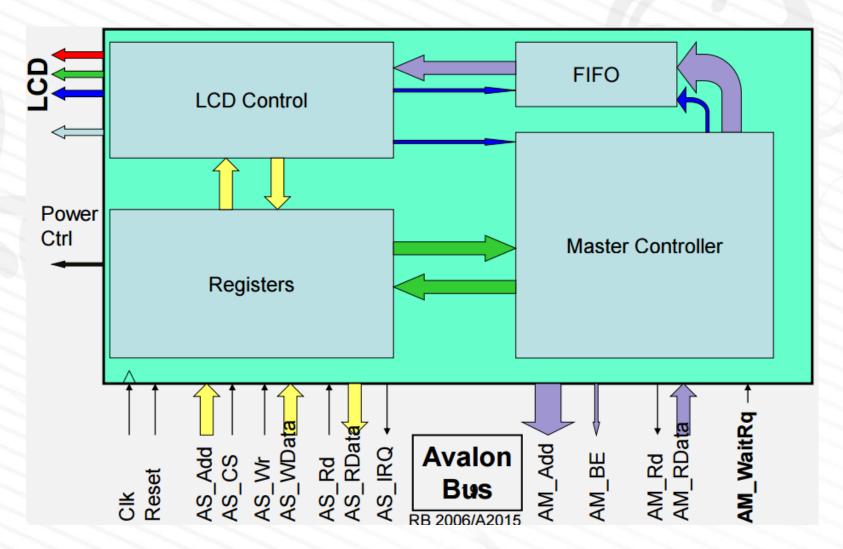

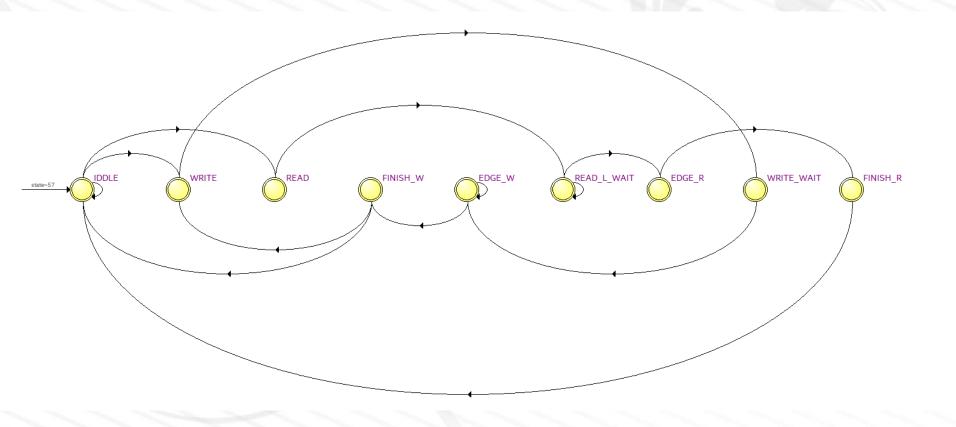

## LCD controller IP block diagram

PS: KEY\_N and IRQAck are not shown here, and some of the pin names maybe slightly different

## **LCD** control

# **Avalon Slave Signals**

# **DMA** engine

```

default values

AM Address

<= (others => '0');

AM ByteEnable <= (others => '0');

AM BurstCount <= (others => '0');

AM Read

<= '0':

dma irq

<= '0':

case dma s is

when waiting => -- waiting for firing the whole DMA frame transfer

if regDmaFire = '1' then

<= avalon:

dma addr <= regDmaStartAddr;

when avalon =>

-- issuing DMA burst transfer

AM Address <= std logic vector(dma addr);

AM ByteEnable <= (others => '1');

AM BurstCount <= std logic vector(regDmaBurstCount);

<= '1';

if AM WaitRequest = '0' then -- the command was successfully sent?

<= transfering;

dma rx cnt <= (others => '0');

end if:

when transfering =>

if dma rx cnt >= regDmaBurstCount then -- transfer received

if unsigned(fifo wrusedw) < regDmaFifoThreshold then -- there is space?

if dma addr >= regDmaEndAddr then -- is the whole frame finished?

dma s <= irqreq;

-- frame not finished, new transfer then

<= avalon;

dma addr <= dma addr + regDmaBurstCount;

end if;

end if:

elsif dma rx d = '1' then -- if transfer not complete and data comes

dma rx cnt <= dma rx cnt + 1;

end if:

when irgreg =>

-- issuing interruption request

dma irq <= '1';

if regDmaIrqAck = '1' then

-- is the interruption acknowleged?

dma s <= waiting;

end if:

when others => null;

end case;

-- delaying cnt value for aligning with fifousedw

dma rx d <= AM ReadValid;

-- sync reset DMA

if regDmaSyncRst = '1' then

dma s <= waiting;

end if;

```

# **Asymetric FIFO**

- Quartus IP

- Asymetric FIFO

- WIDTH IN = 32 bits

- WIDTH OUT = 16 bits

- Show-ahead synchronous

- WR used word flag

- RD used word flag

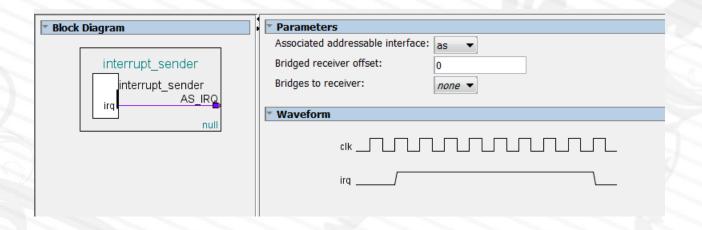

#### **IRQ** interface

PS: According to Avalon Interface Specification, IRQ Acknowledge has to be implementation specific, that is implemented by the user.

0x06 0x18 RW DmaIrqAck

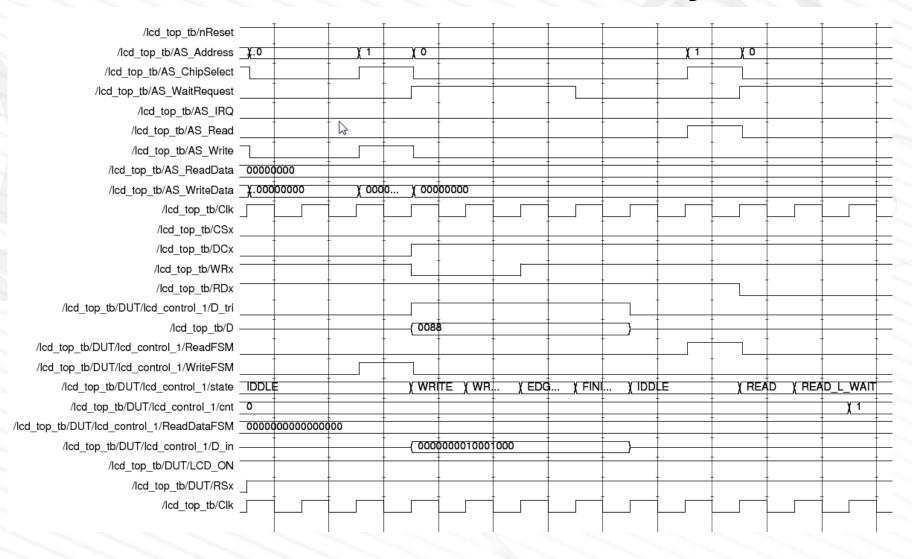

### **Modelsim Simulation Write Cycle**

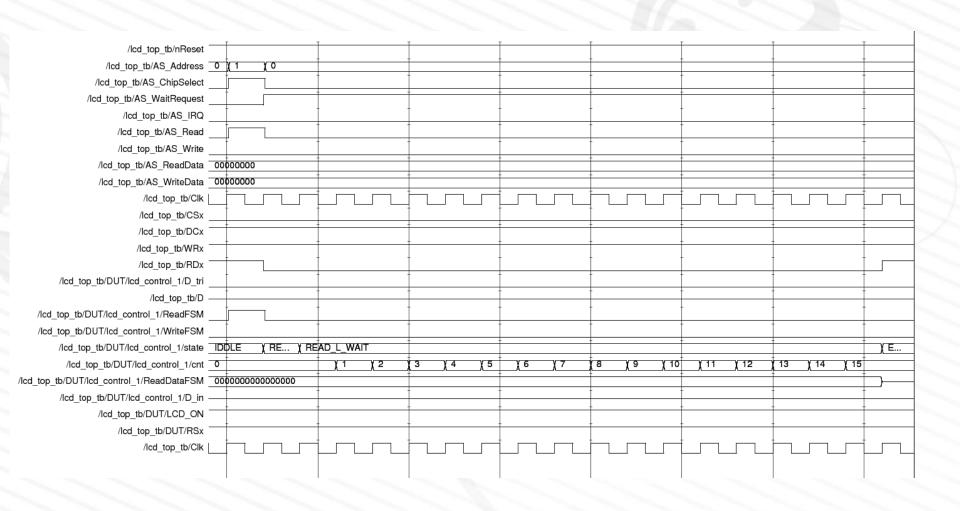

# **Modelsim Simulation Read Cycle**

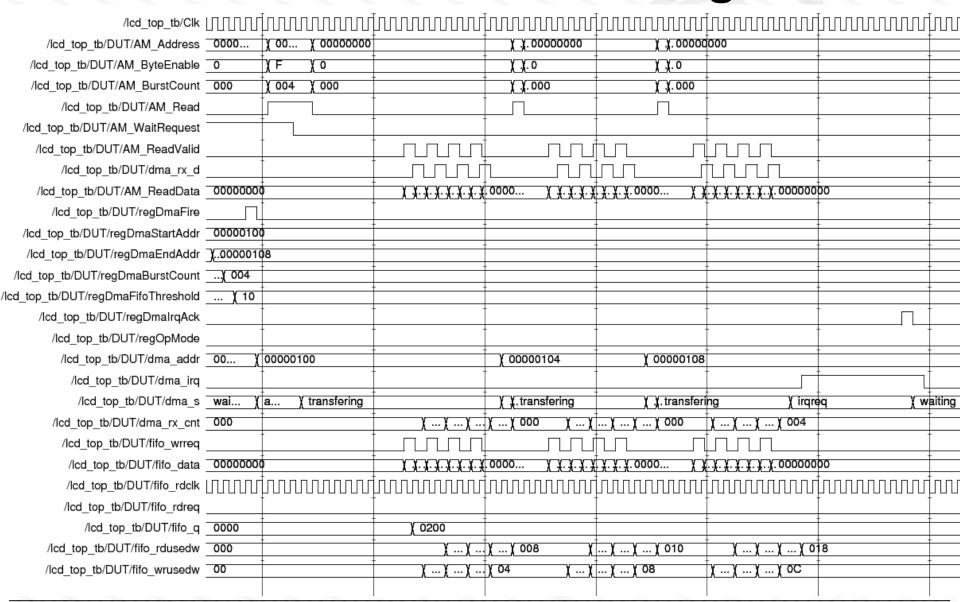

#### **Modelsim Simulation DMA Engine**

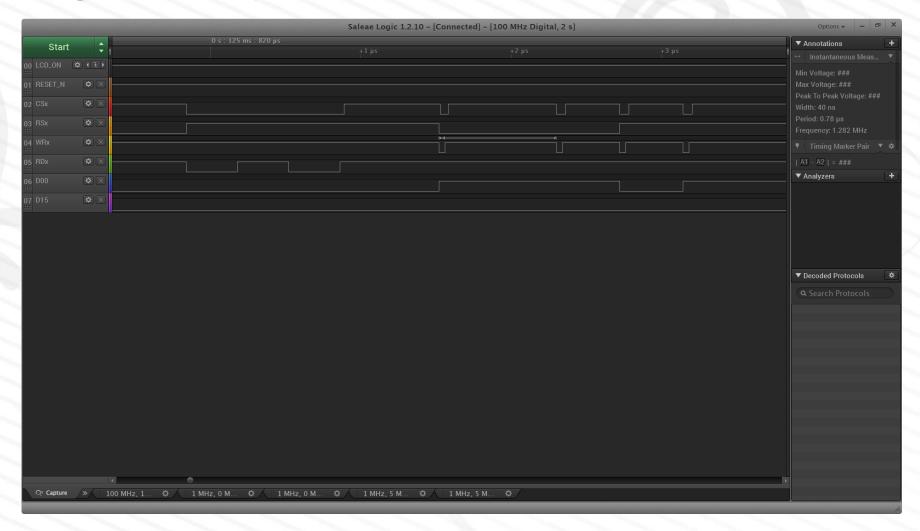

# **Logic Analyser**

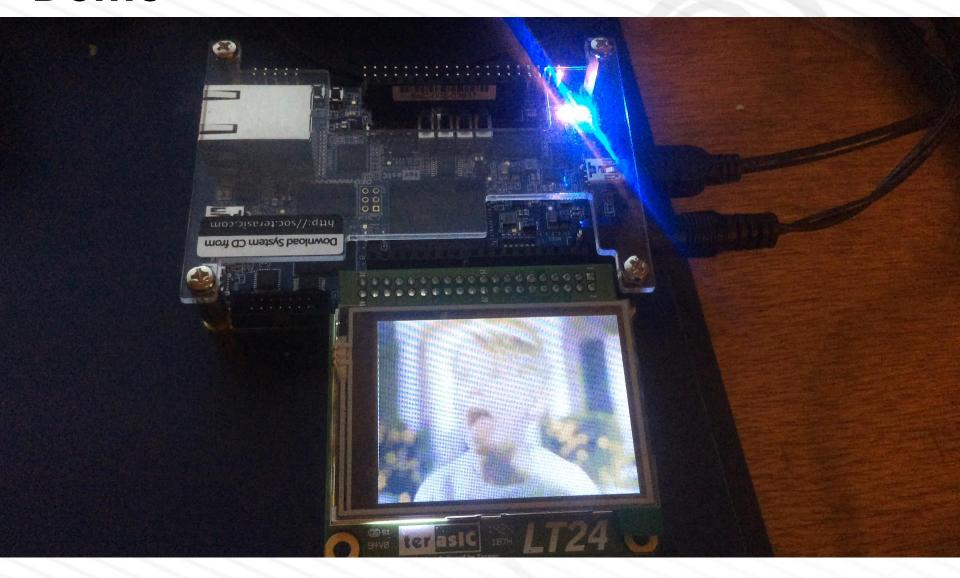

# **Demo**

# **Demo**